Intel PXA26X Manuale Utente Pagina 196

- Pagina / 624

- Indice

- SEGNALIBRI

Valutato. / 5. Basato su recensioni clienti

6-6 Intel® PXA26x Processor Family Developer’s Manual

Memory Controller

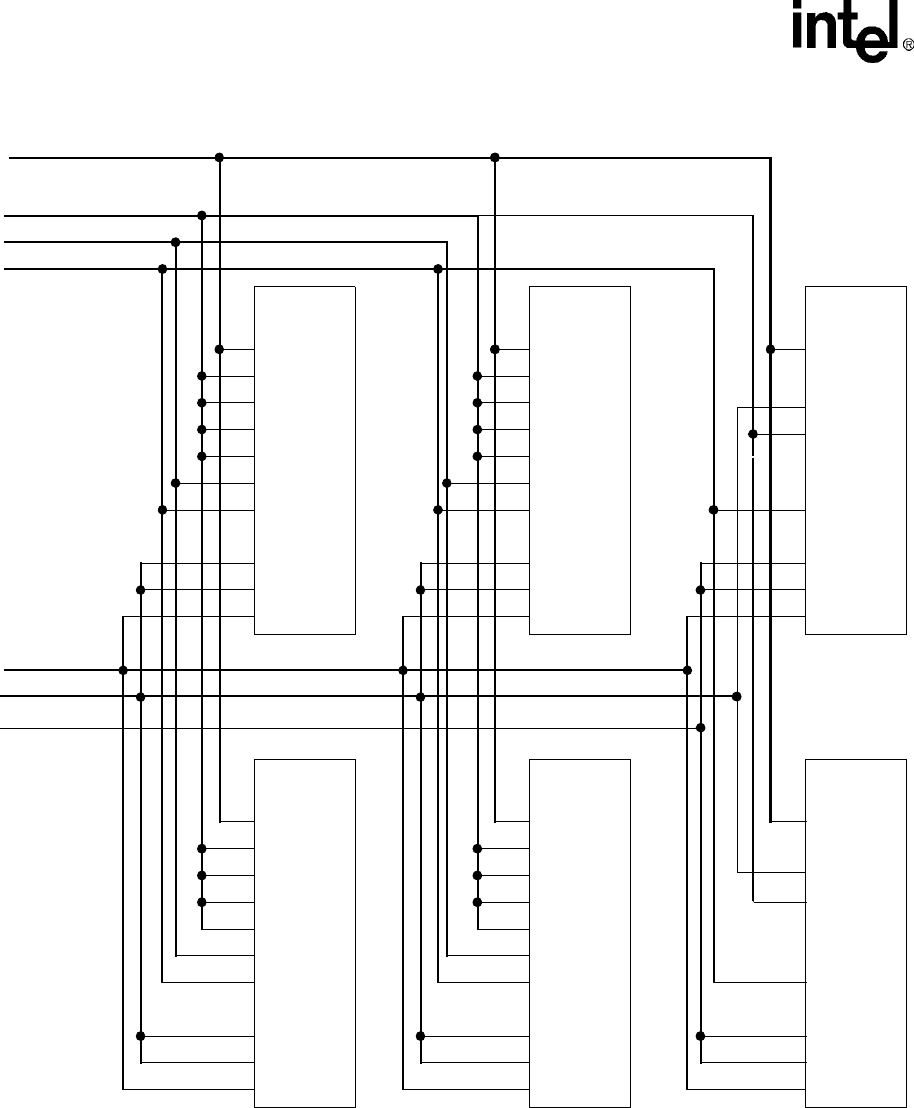

Figure 6-3. Asynchronous Static Memory System Example

6.4 Memory Accesses

If a memory access is followed by an idle bus period, the control signals return to their inactive

state. The address and data signals remain at their previous values to avoid unnecessary bus

transitions and eliminate the need for multiple pull-up resistors.

2Mx16

SMROM

nCS

nRAS

nCAS

CLK

CKE

nMR

addr(12:0)

DQML

DQMH

DQ(15:0)

2Mx16

SMROM

nCS

nRAS

nCAS

CLK

CKE

nMR

addr(12:0)

DQML

DQMH

DQ(15:0)

SRAM

nCS

nOE

nWE

addr(20:0)

DQML

DQMH

DQ(15:0)

2Mx16

SMROM

nCS

nRAS

nCAS

CLK

CKE

nMR

addr(12:0)

DQML

DQMH

DQ(15:0)

2Mx16

SMROM

nCS

nRAS

nCAS

CLK

CKE

nMR

addr(12:0)

DQML

DQMH

DQ(15:0)

SRAM

nCS

nOE

nWE

addr(20:0)

DQML

DQMH

DQ(15:0)

MD(31:0)

nOE

MA(22:2)

SDCLK(0)

nSDRAS, nSDCAS, nWE, CKE(0)

nCS(2:0)

0

0

1

1

2

2

15:0

31:16

DQM[3:0]

31:16

31:16

3

2

1

0

15:0 15:0

22:10

22:10

22:10

22:10

22:2

22:2

0

0

1

1

2

2

3

3

- Developer’s Manual 1

- Contents 2

- Revision History 23

- Introduction 1 25

- 1.2.1 Memory Controller 26

- 1.2.22 Hardware UART (HWUART) 30

- System Architecture 2 31

- 2.2 Package Types 32

- Management 34

- 2.4 Input/Output Ordering 35

- 2.5 Semaphores 36

- 2.6 Interrupts 36

- 2.7 Reset 37

- 2.8 Internal Registers 37

- 2.11 Power Management 38

- 2.12 Pin List 39

- System Architecture 40

- 2.13 Register Address Summary 51

- 2.14 Memory Map 63

- Clocks and Power Manager 3 67

- 3.3 Clock Manager 68

- 3.3.1 32.768-KHz Oscillator 70

- 3.3.2 3.6864-MHz Oscillator 70

- 3.3.3 Core Phase Locked Loop 70

- 3.4 Resets and Power Modes 72

- 3.4.1 Hardware Reset 73

- 3.4.2 Watchdog Reset 73

- 3.4.3 GPIO Reset 74

- 3.4.4 Run Mode 75

- 3.4.5 Turbo Mode 75

- 3.4.6 Idle Mode 76

- 3.4.7 33-MHz Idle Mode 78

- 3.4.9 Sleep Mode 81

- 3.4.9.3 Entering Sleep Mode 83

- 3.4.9.5 Exiting Sleep Mode 85

- 3.4.10 Power Mode Summary 86

- 3.5 Power Manager Registers 88

- PGSR1, PGSR2) 97

- • GPIO reset 99

- • Sleep mode 99

- • Watchdog reset 99

- • Hardware reset 99

- Clocks and Power Manager 100

- 3.6 Clocks Manager Registers 101

- Oscillator 108

- System Integration Unit 4 109

- System Integration Unit 112

- 4.2 Interrupt Controller 130

- Register (ICFP) 134

- 4.3 Real-Time Clock (RTC) 140

- 4.3.3 Trim Procedure 143

- 4.4 Operating System Timer 146

- OSMR2, OSMR3) 147

- 4.5 Pulse Width Modulator 151

- 4.5.2 Register Descriptions 152

- PWM_DUTYn = 6 155

- PWM_PERVALn = 10 (+1) 155

- 4.5.4 Register Summary 156

- DMA Controller 160

- (external) 160

- (internal) 160

- Memory Controller 160

- 5.1.2 Signal Descriptions 161

- • Set zero 163

- • Set three 163

- 5.1.4.2 Descriptor Fetch Mode 165

- (running) 166

- 5.1.5 Channel States 167

- 5.1.6 Read and Write Order 167

- 5.2 Transferring Data 169

- • DCMD[INCTRGADDR] = 1 171

- • DCMD[FLOWSRC] = 1 171

- • DCMD[FLOWTRG] = 0 171

- 5.2.4 Memory-to-Memory Moves 174

- 5.3.1 DMA Interrupt Register 175

- 5.3.7 DMA Command Registers 181

- 5.4 Examples 183

- Locations 186

- Memory Controller 6 191

- 6.2 Functional Description 192

- 6.3 Memory System Examples 194

- 6.4 Memory Accesses 196

- 6.4.1 Reads and Writes 197

- 6.6.1 SDRAM MDCNFG Register 199

- 6.6.3 SDRAM MDREFR Register 204

- Refer to Table 6-6 205

- 6.6.4 SDRAM Memory Options 207

- 6.6.5 SDRAM Command Overview 215

- • Power-Down (PWRDN) 216

- • Enter Self-Refresh (SLFRSH) 216

- • Exit Power-Down (PWRDNX) 216

- • No Operation (NOP) 216

- Figure 6-5. SDRAM Read 217

- Figure 6-9. SDRAM Write 219

- 6.7.1.1 SMROM Memory Options 225

- Configuration Register 226

- CL = 5CL = 5RL = 2RL = 2 228

- 6.8.1 Static Memory Interface 231

- 6.8.3 ROM Interface 238

- MSC0:RDN = 1, MSC0:RRR = 1) 239

- MSC0:RDN = 1, MSC0:RRR = 0) 240

- 6.8.4 SRAM Interface Overview 241

- 6.8.6 FLASH Memory Interface 246

- 6.9.3 16-Bit PC Card Overview 251

- 0ns 50ns 100ns 150ns 257

- 6.10 Companion Chip Interface 258

- 6.10.1.1 GPIO Reset 261

- 6.11.1 Alternate Booting 262

- 6.11.2 Boot Time Defaults 262

- 7.1 Overview 269

- 7.1.1 Features 270

- 7.1.2 Pin Descriptions 272

- 7.2.1 Enabling the Controller 272

- 7.3.1 Input FIFOs 274

- 7.3.2 Lookup Palette 274

- 7.3.4 Output FIFOs 277

- 7.3.6 Direct Memory Access 278

- 7.4.1 External-Palette Buffer 279

- 7.4.2 External-Frame Buffer 280

- • 32 pixels for 1-bit pixels 282

- • 16 pixels for 2-bit pixels 282

- • 8 pixels for 4-bit pixels 282

- • 4 pixels for 8-bit pixels 282

- • 2 pixels for 16-bit pixels 282

- 7.5 Functional Timing 283

- PPL = 319 284

- Line 239 Data Line 0 Data 285

- ENB set to 1 286

- PCP - Pixel Clock Polarity 287

- • DMA bus errors 288

- 7.6.1.2 Branch Mask (BM) 290

- 7.6.1.5 LCD Disable (DIS) 291

- 7.6.1.14 LCD Enable (ENB) 296

- 7.6.2.4 Pixels Per Line (PPL) 298

- 7.6.3.4 Lines Per Panel (LPP) 301

- 7.6.4.2 Bits Per Pixel (BPP) 302

- 7.6.5 LCD Controller DMA 305

- 7.6.5.1 Frame Descriptors 306

- Reserved 307

- 7.6.5.5.1 Load Palette (PAL) 308

- 7.6.7.2 Branch Status (BS) 312

- 7.6.9 TMED RGB Seed Register 314

- Matrix (COAM) 317

- 8.1 Overview 319

- 8.2 Signal Description 319

- 8.3 Functional Description 320

- 8.4 Data Formats 320

- 8.4.1.2 SPI Format Details 322

- 8.6 Baud Rate Generation 325

- 8.7 SSP Serial Port Registers 325

- 8.7.1.2 Frame Format (FRF) 328

- 8.7.2.3 Loop Back Mode (LBM) 330

- Min Max Min Max 333

- 8 Bytes 0 11 3 15 333

- 16 Bytes 0 7 7 15 333

- 8.7.4.7 Transmit FIFO Level 337

- 8.7.4.8 Receive FIFO Level 337

- 9.1 Overview 339

- 9.2 Signal Description 339

- 9.3 Functional Description 339

- 9.3.1 Operational Blocks 341

- 9.3.3.1 START Condition 343

- 9.3.3.3 STOP Condition 344

- 9.4.4 Arbitration 347

- 9.4.4.2 SDA Arbitration 348

- 9.4.5 Master Operations 349

- 9.4.6 Slave Operations 353

- 9.4.7 General Call Address 354

- • Sets the ISR[GCAD] bit 355

- • Sets the ISR[SAD] bit 355

- 9.5.1 Initialize Unit 356

- 9.5.3 Read n Bytes as a Slave 357

- 9.6.1 Initialize Unit 357

- 9.6.3 Read 1 Byte as a Master 358

- 9.7 Glitch Suppression Logic 360

- 9.8 Reset Conditions 360

- 9.9 Register Definitions 360

- C Data Buffer Register- IDBR 361

- C Control Register- ICR 362

- for the following I 363

- Table 9-11. I 363

- C Status Register 364

- Table 9-12. I 365

- Transmitter 10 367

- 10.2 Overview 368

- 10.3 Signal Descriptions 369

- 10.4.1 Reset 371

- – IER (Sheet 1 of 2) 375

- – IER (Sheet 2 of 2) 376

- – LCR (Sheet 1 of 2) 380

- – LCR (Sheet 2 of 2) 381

- – LSR (Sheet 1 of 2) 382

- – LSR (Sheet 2 of 2) 383

- – MCR (Sheet 1 of 2) 384

- – MCR (Sheet 2 of 2) 385

- 10.4.5 DMA Requests 388

- 10.4.6.2 Operation 390

- 10.5 Register Summary 392

- 11.1 Signal Description 395

- 11.2.2 Frame Format 397

- 11.2.3 Address Field 398

- 11.2.4 Control Field 398

- 11.2.5 Data Field 398

- 11.2.6 CRC Field 398

- 11.2.7 Baud Rate Generation 399

- 11.2.8 Receive Operation 399

- 11.2.9 Transmit Operation 400

- Descriptions 402

- 11.3.4 FICP Data Register 406

- 11.3.5 FICP Status Register 0 407

- 11.3.6 FICP Status Register 1 408

- Universal Serial Bus Device 411

- Controller 12 411

- 12.2 Device Configuration 412

- 12.3.1 Signalling Levels 413

- 12.3.2 Bit Encoding 414

- 12.3.3 Field Formats 414

- 12.3.4 Packet Formats 415

- 12.3.4.3 Data Packet Type 416

- 12.3.5 Transaction Formats 417

- 12.3.6 UDC Device Requests 418

- 12.4 UDC Hardware Connection 420

- (optional) 421

- 12.5 UDC Operation 422

- Status Stage 424

- 12.5.7.1 Software Enables DMA 427

- 12.6.1 UDC Control Register 432

- 12, or 14 455

- AC97 Controller Unit 13 463

- 13.3 Signal Description 464

- OUTGOING STREAMS 466

- INCOMING STREAMS 466

- Data PhaseTag Phase 466

- SDATA_OUT 467

- 13.4.1.1 Slot 0: Tag Phase 468

- 13.4.1.7 Slots 6-11: Reserved 470

- 13.4.1.8 Slot 12: I/O Control 470

- 13.4.2.1 Slot 0: Tag Phase 471

- Bit Name Description 473

- 13.5 AC-link Low Power Mode 474

- 13.5.2 Waking up the AC-link 475

- 13.6 ACUNIT Operation 476

- 13.6.1 Initialization 477

- 13.6.2 Trailing bytes 478

- 13.8 Functional Description 479

- 13.8.2 Interrupts 480

- 13.8.3 Registers 480

- • Audio codec registers 481

- • Modem codec registers 481

- AC97 Controller Unit 482

- Controller 14 497

- 14.2 Signal Descriptions 498

- 14.3 Controller Operation 499

- 14.3.4 Transmit FIFO Errors 501

- 14.3.5 Receive FIFO Errors 501

- 14.3.6 Trailing Bytes 501

- 14.5 Data Formats 502

- A8842-01 503

- A8843-01 503

- • Setting ENB to one does: 504

- 14.7 Interrupts 512

- MultiMediaCard Controller 15 513

- 15.2.1 Signal Description 516

- 15.2.4 MMC and SPI Modes 517

- 15.2.4.2 SPI Mode 518

- 15.2.5 Error Detection 519

- 15.2.6 Interrupts 519

- 15.2.7 Clock Control 519

- 15.2.8 Data FIFOs 520

- • Receive 96 bytes of data: 521

- • Receive 98 bytes of data: 521

- • Receive 105 bytes: 521

- • Transmit 96 bytes of data: 522

- • Transmit 98 bytes of data: 522

- • Transmit 105 bytes: 523

- 15.2.8.4 DMA and Program I/O 523

- 15.3.2 Data Transfer 524

- 15.3.2.1 Block Data Write 525

- 15.3.2.2 Block Data Read 525

- Time-out Delay 526

- MMC_RDTO[READ_TO] 526

- 15.3.3 Busy Sequence 527

- 15.3.4 SPI Functionality 527

- 15.4.1 Start and Stop Clock 528

- 15.4.2 Initialize 528

- 15.4.3 Enabling SPI Mode 528

- 15.4.5 Erase 529

- 15.4.7 Single Block Read 530

- 15.4.8 Multiple Block Write 530

- 15.4.9 Multiple Block Read 531

- 15.4.10 Stream Write 531

- 15.4.11 Stream Read 532

- 15.5.1 MMC_STRPCL Register 533

- 15.5.2 MMC_STAT Register 534

- 15.5.3 MMC_CLKRT Register 535

- 15.5.4 MMC_SPI Register 536

- 15.5.5 MMC_CMDAT Register 537

- 15.5.6 MMC_RESTO Register 538

- 15.5.7 MMC_RDTO Register 539

- 15.5.8 MMC_BLKLEN Register 540

- 15.5.9 MMC_NOB Register 540

- 15.5.10 MMC_PRTBUF Register 540

- 15.5.11 MMC_I_MASK Register 541

- 15.5.12 MMC_I_REG Register 542

- 15.5.13 MMC_CMD Register 543

- MultiMediaCard Controller 544

- Table 15-18. MMC_CMD Register 544

- 15.5.14 MMC_ARGH Register 546

- 15.5.15 MMC_ARGL Register 546

- 15.5.18 MMC_TXFIFO FIFO 547

- Protocol Serial Ports 16 549

- 16.3 Signal Description 550

- 16.4 Operation 550

- 16.4.2.1 Time-out 551

- 16.4.3 Data Formats 552

- A9650-01 554

- A9518-02 554

- A9651-01 555

- A9519-02 555

- A9652-01 556

- A9520-02 557

- A9653-01 558

- A9521-02 558

- A9523-02 559

- T1 T2 T3 T4 560

- 16.4.4 Hi-Z on SSPTXD 561

- A9975-01 562

- MSB 4 to 32 Bits LSB 562

- Bit[N] Bit[N-1] Bit[1] Bit[0] 562

- A9976-01 562

- A9977-01 563

- A9978-01 563

- 16.4.5 FIFO Operation 565

- 16.4.6 Baud-Rate Generation 565

- Table 16-4 569

- (Start Delay) 575

- + (Dummy start) 575

- + (Data size) 575

- + (Dummy Stop) 575

- SSTO Bit Definitions 577

- 16.6 Register Summary 582

- Hardware UART 17 585

- 17.2 Features 586

- 17.3 Signal Descriptions 587

- 17.4 Operation 587

- 17.4.1 Reset 589

- 17.4.3 Autoflow Control 591

- can be programmed by the 592

- 17.4.5.1 Operation 593

- (see Table 17-2) 594

- Settings 595

- Hardware UART 616

- Internal Flash 18 617

- Software 618

- 18.1.4 SXCNFG Configuration 618

- Internal Flash 620

(195 pagine)

(195 pagine) (2 pagine)

(2 pagine)

Commenti su questo manuale