Intel FF8062701084601 Scheda Tecnica Pagina 78

- Pagina / 170

- Indice

- SEGNALIBRI

Valutato. / 5. Basato su recensioni clienti

Signal Description

78 Datasheet, Volume 1

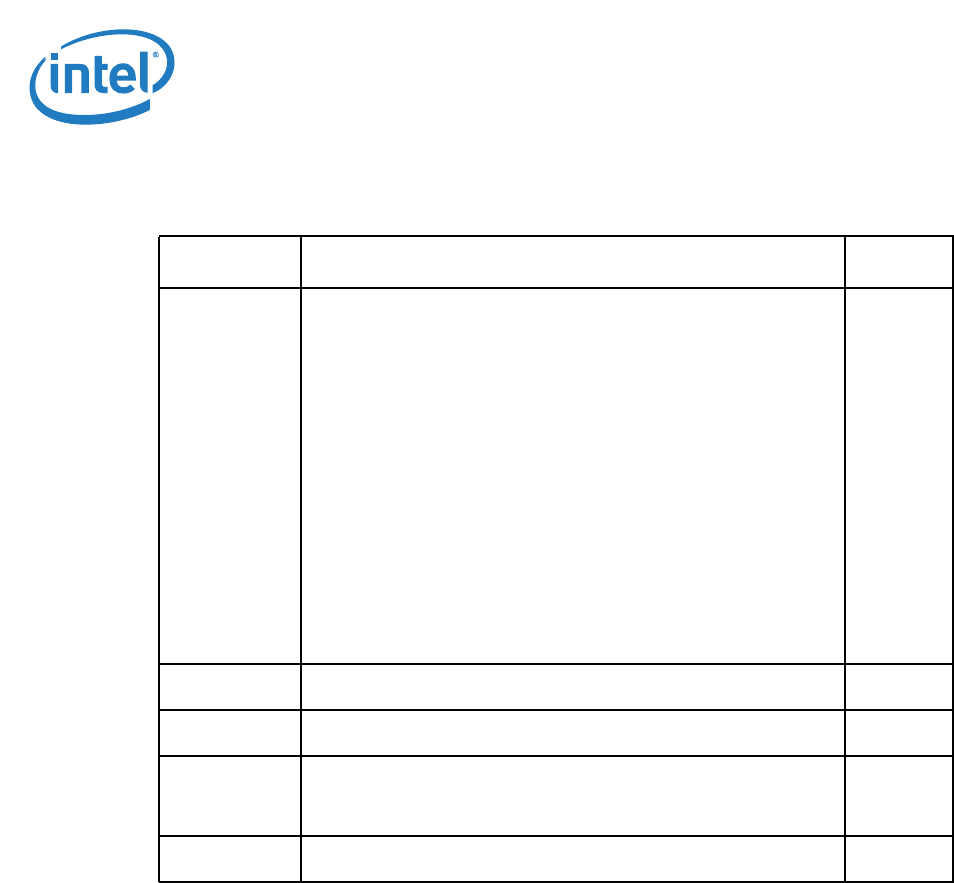

6.3 Reset and Miscellaneous Signals

Table 6-5. Reset and Miscellaneous Signals

Signal Name Description

Direction/

Buffer Type

CFG[17:0]

Configuration Signals: The CFG signals have a default value of '1' if not

terminated on the board.

• CFG[1:0]: Reserved configuration lane. A test point may be placed on

the board for this lane.

• CFG[2]: PCI Express* Static x16 Lane Numbering Reversal

— 1 = Normal operation

— 0 = Lane numbers reversed

• CFG[3]: Reserved

• CFG[4]: eDP enable

— 1 = Disabled

— 0 = Enabled

• CFG[6:5]: PCI Express Bifurcation

— 00 = 1 x8, 2 x4 PCI Express

— 01 = Reserved

— 10 = 2 x8 PCI Express

— 11 = 1 x16 PCI Express

• CFG[17:7]: Reserved configuration lanes. A test point may be placed

on the board for these lands.

I

CMOS

PM_SYNC

Power Management Sync: A sideband signal to communicate power

management status from the platform to the processor.

I

CMOS

RESET#

Platform Reset pin driven by the PCH I

CMOS

RSVD

RSVD_TP

RSVD_NCTF

RESERVED: All signals that are RSVD and RSVD_NCTF must be left

unconnected on the board. However, Intel recommends that all RSVD_TP

signals have using test points.

No Connect

Test Point

Non-Critical

to Function

SM_DRAMRST#

DDR3 DRAM Reset: Reset signal from processor to DRAM devices. One

common to all channels.

O

CMOS

- Datasheet, Volume 1 1

- 2 Datasheet, Volume 1 2

- Contents 3

- 4 Datasheet, Volume 1 4

- Datasheet, Volume 1 5 5

- 6 Datasheet, Volume 1 6

- Datasheet, Volume 1 7 7

- 8 Datasheet, Volume 1 8

- Revision History 9

- 10 Datasheet, Volume 1 10

- 1 Introduction 11

- Introduction 12

- 1.1 Processor Feature Details 13

- 1.2 Interfaces 13

- 1.2.2 PCI Express* 14

- Datasheet, Volume 1 15 15

- 1.2.5 Processor Graphics 16

- 1.3 Power Management Support 17

- 1.5 Package 18

- 1.6 Terminology 18

- 1.7 Related Documents 20

- 2 Interfaces 21

- 2.1.3.1 Single-Channel Mode 22

- Flex Memory Technology Mode 22

- Datasheet, Volume 1 23 23

- Interfaces 23

- 2.1.5.2 Command Overlap 24

- 2.2 PCI Express* Interface 25

- 2.2.1.1 Transaction Layer 26

- 2.2.1.2 Data Link Layer 26

- 2.2.1.3 Physical Layer 26

- 2.2.3 PCI Express Graphics 27

- 2.3.1 DMI Error Flow 28

- 2.3.3 DMI Link Down 29

- 2.4.1.2 3D Pipeline 30

- 2.4.1.3 Video Engine 31

- 2.4.1.4 2D Engine 31

- 2.4.2.1 Display Planes 32

- 2.4.3 Intel 33

- 2.6 Interface Clocking 34

- 3 Technologies 35

- Technologies 36

- Datasheet, Volume 1 37 37

- 3.4 Intel 39

- Turbo Boost Technology 39

- 3.4.2 Intel 40

- 3.7 Intel 41

- 64 Architecture x2APIC 41

- 4 Power Management 43

- (ACPI) States Supported 44

- 4.2.1 Enhanced Intel 46

- SpeedStep 46

- Technology 46

- 4.2.2 Low-Power Idle States 47

- Power Management 48

- 4.2.4 Core C-states 49

- 4.2.5 Package C-States 50

- 4.2.5.1 Package C0 51

- 4.2.5.2 Package C1/C1E 52

- 4.2.5.3 Package C3 State 52

- 4.2.5.4 Package C6 State 52

- Management 53

- Datasheet, Volume 1 55 55

- 4.6 Graphics Power Management 57

- 4.7 Thermal Power Management 59

- 5 Thermal Management 61

- 5.2.1 Intel 62

- Reporting 62

- 5.2.2 Package Power Control 63

- 5.2.3 Power Plane Control 63

- 5.2.4 Turbo Time Parameter 63

- Thermal Management 64

- Datasheet, Volume 1 69 69

- 5.4.1.3 PROCHOT# Signal 71

- 5.4.2.1 On-Demand Mode 73

- 6 Signal Description 75

- Signal Description 76

- Table 6-8. Intel 80

- 6.11 Power Sequencing Signals 82

- 6.12 Processor Power Signals 82

- 6.13 Sense Signals 83

- 7 Electrical Specifications 85

- 7.4 System Agent (SA) V 90

- 7.6 Signal Groups 91

- Table 7-3. Signal Groups 92

- (Sheet 2 of 3) 92

- 7.9 DC Specifications 94

- Table 7-5. Processor Core (V 95

- ±200 mV and the 99

- Electrical Specifications 100

- DC Specifications 101

- Datasheet, Volume 1 103 103

- 8 Processor Pin and Signal 105

- 106 Datasheet, Volume 1 106

- Datasheet, Volume 1 107 107

- 108 Datasheet, Volume 1 108

- Datasheet, Volume 1 109 109

- List by Pin Name 110

- Datasheet, Volume 1 121 121

- 122 Datasheet, Volume 1 122

- Datasheet, Volume 1 123 123

- 124 Datasheet, Volume 1 124

- List by Ball Name 125

- 140 Datasheet, Volume 1 140

- Datasheet, Volume 1 141 141

- 142 Datasheet, Volume 1 142

- Datasheet, Volume 1 143 143

- Datasheet, Volume 1 155 155

- 156 Datasheet, Volume 1 156

- Datasheet, Volume 1 157 157

- 158 Datasheet, Volume 1 158

- Datasheet, Volume 1 159 159

- 160 Datasheet, Volume 1 160

- Datasheet, Volume 1 161 161

- 162 Datasheet, Volume 1 162

- Datasheet, Volume 1 163 163

- 164 Datasheet, Volume 1 164

- Datasheet, Volume 1 165 165

- 166 Datasheet, Volume 1 166

- 9 DDR Data Swizzling 167

- Table – Channel A 168

- Table – Channel B 169

- DDR Data Swizzling 170

(134 pagine)

(134 pagine)

Commenti su questo manuale